Figure 1

### **Contents**

| General description          |    |

|------------------------------|----|

| General description Features |    |

| Typical applications         |    |

| XTR EM 2.4 pin out           |    |

| XTR EM 2.4 pin out           |    |

| European Reference Standards |    |

| Electrical Specifications    |    |

| General Operating Conditions | 4  |

| Electrical Characteristics   |    |

| Functional Overview          |    |

| SPI Communication            |    |

| SPI Commands                 | 8  |

| RAM2 Registers               | 11 |

| Channel Data Rate            |    |

| RF Characteristics           | 14 |

| TX Power Level               |    |

| Aurel catalogue              |    |

| Revision History             |    |

### **General description**

The XTR EM 2.4 is a 1.5kbps to 72kbps low-power, low-voltage chip 2.4GHz ISM band RF transceiver ideal for battery operated wireless applications such as wireless sensors and control. The EM9209's built in custom low power micro-controller supports the proprietary wireless protocol links in the license-free 2.4000GHz to 2.4835GHz ISM band. It includes a low-IF receiver architecture and uses FSK modulation. A SPI interface provides a simple control of the baseband using an external host controller.

The EM9209 provides two communication modes with normal or high sensitivity and programmable bit rate from 1.5kbps to 72kbps. The EM9209 provides a divided clock output programmable at either 32.5kHz or 3.25MHz to drive external micro-controllers time reference.

### **Features**

Low voltage: 1,9 to 3,6 V

Low power: 7mA in RX normal sensitivity mode (NS), 8mA in RX high sensitivity mode (HS).

TX mode: 11mA at -1dBm, 36mA at +10dBm.

- $< 150\mu A$  in stand-by mode.

- < 10nA in power down mode.

- High performance:

- -115dBm sensitivity at 1.5kbps,

- > +10dBm maximum received input signal

- ➤ Programmable output power from -20dBm to +10dBm

- Ultra compact radio design with low BOM cost:

- > COB with 4mm x 4mm footprint

- Operating temperatures: -40°C to +85°C

- Direct antenna interface ( $200\Omega$  differential)

- Low-cost 26MHz crystal oscillator, frequency tolerance over temperature and aging of ±20ppm

- Flexible interface:

- > SPI interface for microcontrollers

- > Fully programmable link layer

## Typical applications

- Remote sensing and control

- Wireless mice, keyboards, toys...

- Wireless watch sensors, sport equipment

- Alarm and security systems

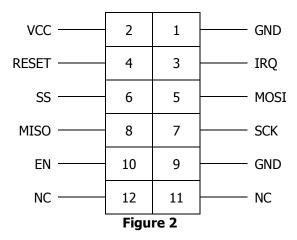

### XTR EM 2.4 pin out

|    | Pin   | Description                                            |

|----|-------|--------------------------------------------------------|

| 1  | GND   | GND connection.                                        |

| 2  | VCC   | Positive Voltage supply connection.                    |

| 3  | IRQ   | Interrupt signal from the radio module.                |

| 4  | RESET | Reset signal (active high) to the radio module.        |

| 5  | MOSI  | Master Out Slave In. SPI signal to the radio module.   |

| 6  | SS    | Slave Select signal (active high) to the radio module. |

| 7  | SCK   | SPI clock to the radio module.                         |

| 8  | MISO  | Master In Slave Out. SPI signal from the radio module. |

| 9  | GND   | GND connection.                                        |

| 10 | EN    | Enable Pin.                                            |

**Table 1 Pin description**

### **Reference Documentation**

The XTR EM 2.4 modules use the EM Microelectronic EM9209 Radio SOC device. For information on technical details of the module such as register settings, timing, application interfaces and clocking refer to the device data sheet available on the website:

http://www.emmicroelectronic.com

Here below the link of the documentation:

http://www.emmicroelectronic.com/products/wireless-rf/proprietary-protocols/em9209

### **European Reference Standards**

The module **XTR EM 2.4** complies with the European standards **EN 300-228**, **EN 300-440** and **EN 301-489** with maximum power supply of 3.6V. The product has been tested according to EN 60950 and can be used inside a special housing that ensures compliance with the above mentioned regulations. The device must be powered by a low voltage safety source protected against short circuits.

The use of the module is foreseen inside housings that assure the overcoming of standards EN 61000 not directly applicable to the module itself. In particular, it is the user's care isolation antenna as the RF output of the transmitter is not able to support directly the electrostatic charges foreseen by the standard EN 61000-4-2.

### **Electrical Specifications**

The device has built-in protection against high static voltages or electric fields; however, anti-static precautions must be taken.

| Parameters                   | Symbol           | Min                   | Max             | Unit |

|------------------------------|------------------|-----------------------|-----------------|------|

| Supply Voltage               | $V_{BAT}$        | -0.3                  | 3.8             | ٧    |

| Input Voltage                | $V_{IN}$         | V <sub>ss</sub> – 0,2 | $V_{BAT} + 0.2$ | V    |

| Electrostatic discharge      | V <sub>ESD</sub> | -1500                 | +1500           | ٧    |

| Maximum Soldering conditions |                  | As per Jedec J        | -STD-020        | ·    |

**Table 2 Absolute maximum rating**

### **General Operating Conditions**

| Parameters                      | Symbol         | Min | Тур | Max | Unit |

|---------------------------------|----------------|-----|-----|-----|------|

| Supply Voltage V <sub>BAT</sub> | $V_{BAT}$      | 1.9 | 2.5 | 3.6 | V    |

| Temperature Range               | T <sub>A</sub> | -40 |     | +85 | °C   |

**Table 3 General Operating condition**

### **Electrical Characteristics**

| Operating<br>Mode | Notes              | Symbol                   | Coditions                           | Min | Тур | Max | Unit |

|-------------------|--------------------|--------------------------|-------------------------------------|-----|-----|-----|------|

| Power Down        |                    | I <sub>VBAT_PWDOWN</sub> | EN_REG = 0                          |     |     | 1   | μΑ   |

| Standby           |                    | I <sub>VBAT_STDBY</sub>  | 26MHz crystal oscillator disabled   |     | 140 |     | μΑ   |

| Auto-calibration  |                    | I <sub>AUTOCAL</sub>     | Auto-calibration mode               |     | 4.2 |     | mA   |

| Tue in our it     |                    | I <sub>VBAT_TX3</sub>    | P <sub>OUT</sub> = 1.1 dBm, 2440MHz |     | 11  |     | mA   |

| Transmit          | 1                  | I <sub>VBAT_TX7</sub>    | P <sub>OUT</sub> = 10 dBm, 2440MHz  |     | 36  |     | mA   |

| Rossius           | Normal sensitivity | I <sub>VBAT_RXNS</sub>   | 2440 MHz                            |     | 7   |     | mA   |

| Receive           | High sensitivity   | I <sub>VBAT_RXHS</sub>   | 2440 MHz                            |     | 8   |     | mA   |

### Table 4 Supply currents on V<sub>BAT</sub>

Note 1: See Table 9 for further clarifications

### **Functional Overview**

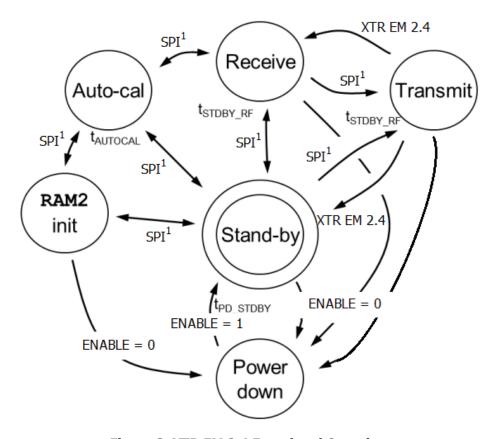

Figure 3 XTR EM 2.4 Functional Overview

Notes:

### **Power Down**

This mode is enabled when ENABLE is tied to  $V_{SS}$  or left floating (3 $\mu$ A pull down). All regulators and the voltage reference are disabled and the supply current is in the nA range.

### **Standby Mode**

When ENABLE is high the XTR EM 2.4 wakes up in standby mode at about  $t_{\text{PD-STBY}}$  seconds (see Table 5). The SPI register memory is then set to 0 and it waits for new configuration. In standby mode all internal circuits are disabled and can be accessed.

### **RAM2 Init**

The XTR EM 2.4 can be configured using a 16 registers memory RAM2. The RAM is resetted to 0 when ENABLE is set. In order to avoid 16 different write cycles, a dedicated subroutine located at ROM\_BOOT\_Address = 0 will initialize most RAM2 addresses to their default values.

<sup>1.</sup> See SPI Communication chapter, page 6.

### User guide - PRELIMINARY VERSION

### Auto-cal

### VCO center frequency

Due to temperature variations the XTR EM 2.4 frequency synthesizer has an auto calibration mode that must run periodically via SPI command; this procedure assures that the FSK modulator is kept operating and whitin specification. Tipically, an auto calibration procedure should be run when a changing channel or a temperature variation (more than 10°C) occurs.

#### PTAT reference current

The internally generated PTAT current can be self calibrated using an internal PTAT generator.

### **Transmit**

During the transmission routine the XTR EM 2.4 outputs a FSK-modulated packet, it returns to receive mode or standby mode with the crystal oscillator enabled and sets the interrupt pin IRQ high. Depending on the subroutine previously set (in the RAM2 Init procedure) the XTR EM 2.4 can transmit the whole TXFIFO (till TXFIFO size is 0) or a predefined number of bytes programmed in RAM2.

Transmit operation can be set using the SPI command Send TXFIFO.

### Receive

The XTR EM 2.4 in receive mode waits for a FSK-modulated packet. After receiving a suitable packet it sets the IRQ pin high. Depending on the programmed subroutine, it can either read the size of the packet to be received in the header or in RAM2.

| Parameter                 | Notes | Symbol               | Min  | Тур | Max | Unit |

|---------------------------|-------|----------------------|------|-----|-----|------|

| Standby mode → TX/RX mode | 1     | t <sub>STBY-RF</sub> | 0.8  | 1   | 10  | ms   |

| Power Down → Standby mode |       | t <sub>PD-STBY</sub> | 1000 |     |     | μs   |

| Auto calibration          |       | T <sub>AUTOCAL</sub> | 340  |     |     | μs   |

Table 5 Timing characteristics (VBAT = 2.5V)

Note 1: Dominated by the crystal oscillator startup time, which strongly depends on the quartz Q-factor.

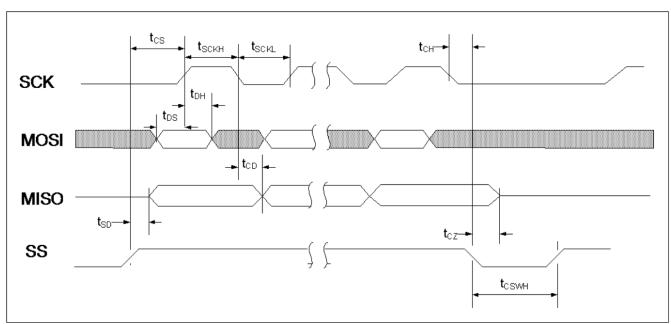

### **SPI Communication**

The XTR EM 2.4 has an SPI interface supporting communication between an application microcontroller and one or more slave devices with the SPI standards. The SPI interface is used to read from and to write into all the registers.

SPI operations allow various accesses:

- Memories write and read actions

- Micro-controller commands

- Loading of subroutines in RAM1

- Test instructions (used in production)

A SPI transaction is defined as all of the activity on SCK, MOSI and MISO that occurs between one rising edge of SS and its next falling edge. All the data shall be sent starting with the MSB first. Not all the commands are encoded on a number of bits multiple of 8. Additional clocks can be sent after the command with no impact on the command decoding. Thus, the chip can be accessed without problems

using an 8-bit wide SPI interface. Each change to MOSI is latched on the rising edge of SCK, and each change to MISO is available on the falling edge of SCK. A timing diagram is shown in Figure 4. Complete timing specifications are given in Table 6.

Figure 4 SPI timing diagram

| Symbol            | Parameters        | Min | Max | Units |

|-------------------|-------------------|-----|-----|-------|

| t <sub>DS</sub>   | MOSI to SCK Setup | 20  |     | ns    |

| t <sub>DH</sub>   | SCK to MOSI hold  | 20  |     | ns    |

| $t_{SD}$          | SS to MISO Valid  |     | 30  | ns    |

| t <sub>CD</sub>   | SCK to MISO Valid |     | 30  | ns    |

| $t_{SCKL}$        | SCK low time      | 40  |     | ns    |

| t <sub>SCKH</sub> | SCK high time     | 40  |     | ns    |

| $f_{sck}$         | SCK frequency     | 0   | 10  | MHz   |

| t <sub>CS</sub>   | SS to SCK Setup   | 20  |     | ns    |

| t <sub>CH</sub>   | SCK to SS Hold    | 20  |     | ns    |

| t <sub>CSWH</sub> | SS Inactive Time  | 20  |     | ns    |

| t <sub>CZ</sub>   | SS to MISO High Z |     | 30  | ns    |

**Table 6 SPI timing values**

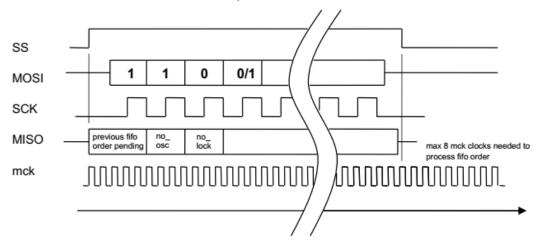

For each SPI command, MISO will always give three status bits on the first three SCK cycles.

- As soon as SS goes high, the first status bit (Status[2]) is available on the MISO terminal. This bit is called "Previous\_FIFO\_Order\_Pending" and is high when the microcontroller has not yet processed the previous FIFO order. This process takes a maximum of 8 clock cycles and starts on the falling edge of the SS signal.

- Status[1] reflects the inactivity of the crystal oscillator (0: running).

- Status[0] shows the unlock state of the 2.4GHz LO frequency synthesizer (0: main LO PLL locked).

For connect transmission operation, status[2..0] must be equal to '000'.

The technical characteristics can change without notice. AUR°EL S.p.A doesn't assume the responsibility to the damages caused by an improper use of the device.

Condition: 25°C, 2.5V, 25pF

### User guide - PRELIMINARY VERSION

### **SPI Commands**

### Read\_RXFIFO

| MOSI | 1    | 1     | 0   | 0    | х     | х     | х   | х | х    | х     | х     | х   | Х | х | х | х |

|------|------|-------|-----|------|-------|-------|-----|---|------|-------|-------|-----|---|---|---|---|

| MISO | Stat | us[2. | .0] | RXFI | FO_Si | ze[4. | .0] |   | RXFI | FO_Da | ta[7. | .0] |   |   |   |   |

This command returns the next byte out of the RXFIFO. It also returns the total number of bytes currently available in the RXFIFO (including the one being read).

This SPI operation works together with the internal microcontroller and is functional only when this latter has been started (SPI command Start\_Micro) and when the master clock is active (Crystal oscillator must be enabled). The order is taken into account only when SS signal goes down and the RXFIFO size information are sampled when SS is low.

Figure 5 Timing of the SPI Read\_RXFIFO / Write\_TXFIFO command

#### Write TXFIFO

| MOSI | 1    | 1     | 0   | 1    | TXFIFO_Data[70]           |     | х | х | х | х |

|------|------|-------|-----|------|---------------------------|-----|---|---|---|---|

| MISO | Stat | us[2. | .0] | RXFI | FO_Size[40] TXFIFO_Size[4 | .0] |   | х | х | х |

This command writes a byte to the TXFIFO. It also returns the total number of bytes in both FIFOs, not including this one. This SPI operation works together whit the internal microcontroller and is functional only when this latter has been started (SPI command Start\_Micro) and when the master clock is active (Crystal oscillator must be enabled). The order is taken into account only when SS signal goes down and the FIFO size information are sampled by mck when SS is low.

### Read\_RXFIFO\_Size

| MOSI | 1    | 1     | 1   | 0 | 0 | 0 | 0 | х    | х     | х     | х   | х | х | х | х | х |

|------|------|-------|-----|---|---|---|---|------|-------|-------|-----|---|---|---|---|---|

| MISO | Stat | us[2. | .0] | Х | х | х | х | RXFI | FO_Si | ze[4. | .0] |   | х | х | х | х |

This command reads the total number of bytes currently available in the RXFIFO.

### Read\_TXFIFO\_Size

| MOSI | 1    | 1     | 1   | 0 | 0 | 0 | 1 | х    | х     | х     | х   | х | х | х | х | х |

|------|------|-------|-----|---|---|---|---|------|-------|-------|-----|---|---|---|---|---|

| MISO | Stat | us[2. | .0] | х | х | х | х | TXFI | FO_Si | ze[4. | .0] |   | х | х | х | х |

This command reads the total number of bytes currently available in the TXFIFO.

### XTR EM 2.4

### User guide - PRELIMINARY VERSION

#### Read\_RAM1

| MOSI | 0 | 0 | 1 | ado | address[50] |   |   |   |   |     |       | х     | х   | х | х | х | х | х | х | х | х | х | х | х |

|------|---|---|---|-----|-------------|---|---|---|---|-----|-------|-------|-----|---|---|---|---|---|---|---|---|---|---|---|

| MISO |   |   |   |     | х           | х | х | х | х | dat | ta_re | ead[' | 110 | ] |   |   |   |   |   |   |   | х | х | х |

This command reads the 12 bits word from the specified address (6bits) of RAM1. This command will put the microcontroller on hold and reset state, until last bit has been processed.

### Write\_RAM1

| MOSI | 0    | 0    | 0  | ad | dres | s[5 | 0] |   |   | dat | ta_w | rite[ | 110 | )] |   |   |   |   |   |   |   | х | х | х |

|------|------|------|----|----|------|-----|----|---|---|-----|------|-------|-----|----|---|---|---|---|---|---|---|---|---|---|

| MISO | Stat | us[2 | 0] | х  | х    | х   | х  | х | х | х   | х    | х     | х   | х  | х | х | х | х | х | х | х | х | х | х |

This command writes a 12 bits word to the specified address (4 bits) of RAM1. This command will put the microcontroller on hold and reset state until last bit has been processed.

### Read RAM2

| MOSI | 0    | 1     | 1  | ado | dress | [30 | )] | х   | х    | х     | х   | х | х | х | х | х | х | х | х | х | х | х | х | х |

|------|------|-------|----|-----|-------|-----|----|-----|------|-------|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|

| MISO | Stat | tus[2 | 0] | Х   | Х     | х   | Х  | dat | a_re | ead[1 | 110 | ] |   |   |   |   |   |   |   | х | Х | Х | х | х |

This command reads the 12 bits word to the specific address (4 bits) of RAM2. This command will put the microcontroller on hold until last bit has been processed.

### • Write\_RAM2

| MOSI | 0    | 1    | 0  | ado | dres | s[3 | 0] | dat | ta_w | rite[ | 110 | )] |   |   |   |   |   |   |   | х | х | х | х | х |

|------|------|------|----|-----|------|-----|----|-----|------|-------|-----|----|---|---|---|---|---|---|---|---|---|---|---|---|

| MISO | Stat | us[2 | 0] | Х   | Х    | х   | х  | х   | Х    | х     | х   | х  | х | х | х | Х | х | х | х | х | х | х | х | х |

This command writes a 12 bits word to the specified address (4 bits) of RAM2. This command will put the microcontroller on hold until last bit has been processed.

### Reset\_Micro

| - | MOSI | 24-4   | 1    | 1 | 0 | 0 | 1 | 0 | Х |

|---|------|--------|------|---|---|---|---|---|---|

|   | MISO | Status | [20] |   | X | X | X | X | X |

This instruction allows an asynchronous reset of the microcontroller. Never use this command when the micro is running (RAM2 and FIFO's content could be corrupted). Always first stop the micro using SPI command Stop Micro prior to use Reset Micro.

### Stop\_Micro

| MOSI | 1     | 1    | 1 | 0 | 0 | 1 | 1 | х |

|------|-------|------|---|---|---|---|---|---|

| MISO | Statu | s[20 | ] | х | х | х | x | х |

This command stops the microcontroller.

### • Start\_Micro

| MOSI | 1     | 1    | 1 | 0 | 1 | 0 | 0 | Х |

|------|-------|------|---|---|---|---|---|---|

| MISO | Statu | s[20 | ] | х | х | х | х | х |

This command start the microcontroller and executes the program currently stored in RAM1.

### User guide - PRELIMINARY VERSION

#### Clear\_IRQ

| MOSI | 1     | 1    | 1 | 0 | 1 | 0 | 1 | х |

|------|-------|------|---|---|---|---|---|---|

| MISO | Statu | s[20 | ] | х | х | х | х | х |

Use this command to reset the IRQ signal. It works only when microcontroller is running.

### Send\_TXFIFO

| 1 | MOSI | 1     | 1    | 1 | 0 | 1 | 1 | 0 | х |

|---|------|-------|------|---|---|---|---|---|---|

| 1 | MISO | Statu | s[20 | ] | х | Х | х | Х | х |

This command will send the current contents of the TXFIFO. Depending on the selected subroutine, the program either sends the full content of the FIFO, or the number of bytes specified in RAM2.

### Aux\_com

| MOSI | 1     | 1    | 1 | 0 | 1 | 1 | 1 | х |

|------|-------|------|---|---|---|---|---|---|

| MISO | Statu | s[20 | ] | х | х | х | х | х |

This command allows the Channel RSSI to be read and stored to Limit\_RSSI[3:0].

#### ROM Boot

| MOSI | 1    | 1     | 1  | 1 | 0 | 0 | 0 | ROM | Boot_ | Addr | ess[8 | 0] |   |   |   |   |

|------|------|-------|----|---|---|---|---|-----|-------|------|-------|----|---|---|---|---|

| MISO | Stat | us [2 | 0] | х | х | х | х | х   | х     | х    | х     | х  | х | х | х | х |

This command copies the 64 12 bits instructions from the specified ROM address to RAM1. This allows for fast initialization of the microcontroller subroutines.

The crystal oscillator must be enabled to perform this operation. Additionally, ROM\_Boot command stops and resets the microcontroller.

### • ROM\_Boot0\_and\_Start

| MOSI | 1     | 1    | 1 | 1 | 1 | 1 | 1 | х |

|------|-------|------|---|---|---|---|---|---|

| MISO | Statu | s[20 | ] | x | x | x | x | x |

This command copies the 64 12-bits instructions from the ROM address 0 to RAM1. This allows for fast initialization of the microcontroller subroutines.

The crystal oscillator must be enabled to perform this operation. Additionally, ROM\_Boot0\_and\_Start command resets and starts the microcontroller. It goes in standby mode.

### **XTR EM 2.4** User guide - PRELIMINARY VERSION

# **RAM2 Registers**

In this section are shown all the most relevant RAM2 Register in order to properly configure the XTR EM 2.4.

|   | Bit position          | 11                             | 10                             | 9                               | 8                 | 7             | 6    | 5     | 4                  | 3                                          | 2                           | 1                            | 0                |

|---|-----------------------|--------------------------------|--------------------------------|---------------------------------|-------------------|---------------|------|-------|--------------------|--------------------------------------------|-----------------------------|------------------------------|------------------|

|   | Default<br>Value      | 1                              | 1                              | 1                               | 1                 | 1             | 1    | 0     | 0                  | 0                                          | 1                           | 0                            | 0                |

| 0 | Reset Value           | 0                              | 0                              | 0                               | 0                 | 0             | 0    | 0     | 0                  | 0                                          | 0                           | 0                            | 0                |

|   |                       | VDD_Synth<br>_En               | VDD_RXTX<br>_En                | Xtal_En                         |                   | Rese          | rved |       | Div_Ck_Fre<br>q[0] | Div_Ck_Fre<br>q[1]                         |                             | Reserved                     |                  |

|   | Description           | Voltage<br>Regulator<br>Enable | Voltage<br>Regulator<br>Enable | Crystal<br>Oscillator<br>Enable |                   | Rese          | rved |       | clock output o     | equency of the on DIV_CK (see point)       |                             | Reserved                     |                  |

|   |                       | Endoic                         | Endoic                         | Endoic                          | L                 |               |      |       | tcst               | politicy                                   | 1                           |                              |                  |

|   | Bit position          | 11                             | 10                             | 9                               | 8                 | 7             | 6    | 5     | 4                  | 3                                          | 2                           | 1                            | 0                |

|   | Default<br>Value      | 0                              | 0                              | 0                               | 0                 | 0             | 0    | 0     | 0                  | 0                                          | 0                           | 0                            | 0                |

| 1 | Reset Value           | 0                              | 0                              | 0                               | 0                 | 0             | 0    | 0     | 0                  | 0                                          | 0                           | 0                            | 0                |

|   |                       |                                |                                |                                 |                   | Reserved      |      |       |                    |                                            | TX_On                       | RX_On                        | Reserved         |

|   | Description           | Voltage<br>Regulator<br>Enable | Voltage<br>Regulator<br>Enable | Crystal<br>Oscillator<br>Enable |                   | Rese          | rved |       | clock output o     | equency of the<br>on DIV_CK (see<br>point) |                             | Reserved                     |                  |

|   |                       | Litable                        | Litable                        | Endoic                          |                   |               |      |       |                    | pomey                                      | 1                           |                              |                  |

|   | Bit position          | 11                             | 10                             | 9                               | 8                 | 7             | 6    | 5     | 4                  | 3                                          | 2                           | 1                            | 0                |

|   | Default<br>Value      | 1                              | 0                              | 1                               | 0                 | 0             | 0    | 0     | 1                  | 0                                          | 1                           | 0                            | 1                |

| 2 | Reset Value           | 0                              | 0                              | 0                               | 0                 | 0             | 0    | 0     | 0                  | 0                                          | 0                           | 0                            | 0                |

|   | Description           |                                |                                |                                 |                   |               | Rese | erved |                    |                                            |                             |                              |                  |

|   | Description           |                                |                                |                                 |                   |               | Rese | erved |                    |                                            |                             |                              |                  |

|   |                       | Т                              | ı                              |                                 | Т                 | Г             |      | Т     | 1                  | 1                                          | ı                           | 1                            |                  |

|   | Bit position          | 11                             | 10                             | 9                               | 8                 | 7             | 6    | 5     | 4                  | 3                                          | 2                           | 1                            | 0                |

|   | Default<br>Value      | 0                              | 0                              | 1                               | 0                 | 1             | 1    | 0     | 0                  | 1                                          | 0                           | 0                            | 0                |

| 3 | Reset Value           | 0                              | 0                              | 0                               | 0                 | 0             | 0    | 0     | 0                  | 0                                          | 0                           | 0                            | 0                |

|   | Description           |                                |                                |                                 | Rese              | erved         |      |       |                    | VCO_Code<br>[3]                            | VCO_Code<br>[2]             | VCO_Code<br>[1]              | VCO_Code<br>[0]  |

|   | ,                     |                                |                                |                                 | Rese              | erved         |      |       |                    | The VCO tuning                             |                             | ed automatically by<br>edure | auto-calibration |

|   |                       |                                | 10                             | 0                               |                   | -             |      |       |                    | 2                                          |                             |                              | 0                |

|   | Bit position  Default | 11                             | 10                             | 9                               | 8                 | 7             | 6    | 5     | 4                  | 3                                          | 2                           | 1                            | 0                |

|   | Value                 | 0                              | 1                              | 1                               | 0                 | 1             | 0    | 0     | 0                  | 0                                          | 0                           | 0                            | 0                |

| 4 | Reset Value           | O<br>I_Pre_PA                  | O<br>I_Pre_PA                  | O<br>I_Pre_PA                   | O<br>I_Pre_PA     | O<br>I_Pre_PA | 0    | 0     | 0                  | 0                                          | 0                           | 0                            | 0                |

|   | Description           | [4]                            | [3]                            | [2]                             | [1]               | [0]           |      |       |                    | Reserved                                   |                             |                              |                  |

|   |                       | Current                        | bias of the PA prea            | mplifier. Defines R             | F Output power in | TX mode       |      |       |                    | Reserved                                   |                             |                              |                  |

|   | Bit position          | 11                             | 10                             | 9                               | 8                 | 7             | 6    | 5     | 4                  | 3                                          | 2                           | 1                            | 0                |

|   | Default<br>Value      | 0                              | 1                              | 0                               | 0                 | 0             | 1    | 0     | 0                  | 1                                          | 0                           | 0                            | 0                |

| 5 | Reset Value           | 0                              | 0                              | 0                               | 0                 | 0             | 0    | 0     | 0                  | 0                                          | 0                           | 0                            | 0                |

|   |                       |                                | <u> </u>                       | <u> </u>                        | l .               | erved         |      |       | ı <u> </u>         | Main_PTAT                                  | Main_PTAT                   | Main_PTAT                    | Main_PTAT        |

|   | Description           |                                |                                |                                 |                   | erved         |      |       |                    | [3]                                        | [2]<br>ontrol of the main o | [1]<br>thip PTAT current b   | [0]              |

|   | 1                     | I                              |                                |                                 |                   |               |      |       |                    | I                                          |                             |                              |                  |

# XTR EM 2.4 User guide – PRELIMINARY VERSION

|    | Bit position          | 11                                    | 10                   | 9                 | 8                 | 7                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                | 4        | 3                 | 2                 | 1                 | 0                 |  |  |

|----|-----------------------|---------------------------------------|----------------------|-------------------|-------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------|-------------------|-------------------|-------------------|-------------------|--|--|

|    | Default<br>Value      | 0                                     | 1                    | 0                 | 1                 | 1                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                | 0        | 0                 | 0                 | 0                 | 0                 |  |  |

| 6  | Reset Value           | 0                                     | 0                    | 0                 | 0                 | 0                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                | 0        | 0                 | 0                 | 0                 | 0                 |  |  |

|    | Description           | I_PA<br>[4]                           | I_PA<br>[3]          | I_PA<br>[2]       | I_PA<br>[1]       | I_PA<br>[0]                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |          | Reserved          |                   |                   |                   |  |  |

|    | Description           | Curre                                 | nt bias of the PA. [ | Defines RF Output | Power in Transmit | mode                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |          | Reserved          |                   |                   |                   |  |  |

|    |                       |                                       |                      |                   |                   |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |          |                   |                   |                   |                   |  |  |

|    | Bit position          | 11                                    | 10                   | 9                 | 8                 | 7                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                | 4        | 3                 | 2                 | 1                 | 0                 |  |  |

|    | Default<br>Value      | 1                                     | 0                    | 0                 | 1                 | 0                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                | 0        | 0                 | 0                 | 0                 | 0                 |  |  |

| 7  | Reset Value           | 0                                     | 0                    | 0                 | 0                 | 0                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                | 0        | 0                 | 0                 | 0                 | 0                 |  |  |

|    | Description           |                                       | Reserved             |                   |                   |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |          |                   |                   |                   |                   |  |  |

|    | Description           |                                       | Reserved             |                   |                   |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |          |                   |                   |                   |                   |  |  |

|    |                       |                                       |                      |                   | -                 |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |          |                   |                   |                   |                   |  |  |

|    | Bit position          | 11                                    | 10                   | 9                 | 8                 | 7                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                | 4        | 3                 | 2                 | 1                 | 0                 |  |  |

| 8  | Default<br>Value      | 0                                     | 1                    | 0                 | 0                 | 1                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                | 0        | 0                 | 0                 | 0                 | 0                 |  |  |

|    | Reset Value           | 0                                     | 0                    | 0                 | 0                 | 0                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                | 0        | 0                 | 0                 | 0                 | 0                 |  |  |

|    | Description           |                                       | Reserved             |                   |                   |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RB_Inst_Di<br>s                                  | Reserved | Limit_RSSI<br>[3] | Limit_RSSI<br>[2] | Limit_RSSI<br>[1] | Limit_RSSI<br>[0] |  |  |

|    | Description           |                                       | Reserved             |                   |                   |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ROMBoot<br>Instruction<br>Disable                | Reserved |                   | RSSI              | Value             |                   |  |  |

|    |                       |                                       | T                    | Т                 |                   | Т                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Г                                                |          | Т                 | Т                 | Т                 |                   |  |  |

|    | Bit position          | 11                                    | 10                   | 9                 | 8                 | 7                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                | 4        | 3                 | 2                 | 1                 | 0                 |  |  |

|    | Default<br>Value      | 1                                     | 0                    | 1                 | 0                 | 0                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                | 0        | 0                 | 0                 | 0                 | 0                 |  |  |

| 9  | Reset Value           | 0                                     | 0                    | 0                 | 0                 | 0                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                | 0        | 0                 | 0                 | 0                 | 0                 |  |  |

|    | Description           | Reserved DFT_Mes [7]                  |                      |                   |                   |                                                          | DFT_Mes         DFT_Mes         DFT_Mes         DFT_Mes         DFT_Mes         DFT_Mes         DFT_Mes         DFT_Mes         DFT_Mes         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I |                                                  |          |                   |                   |                   |                   |  |  |

|    |                       | Reserved                              |                      |                   |                   | Error frequency measured by DFT in High Sensitivity mode |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |          |                   |                   |                   |                   |  |  |

|    |                       |                                       | ı                    | T                 |                   | T                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <del>                                     </del> |          |                   |                   | T                 |                   |  |  |

|    | Bit position          | 11                                    | 10                   | 9                 | 8                 | 7                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                | 4        | 3                 | 2                 | 1                 | 0                 |  |  |

|    | Default<br>Value      | 0                                     | 0                    | 0                 | 0                 | 1                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                | 0        | 0                 | 0                 | 0                 | 0                 |  |  |

| 10 | Reset Value           | 0                                     | 0                    | 0                 | 0                 | 0                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                | 0        | 0                 | 0                 | 0                 | 0                 |  |  |

|    | Description           |                                       |                      |                   |                   |                                                          | Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | erved                                            |          |                   |                   |                   |                   |  |  |

|    |                       | Reserved                              |                      |                   |                   |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  |          |                   |                   |                   |                   |  |  |

|    |                       |                                       |                      |                   |                   |                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _ 1                                              |          | _                 | _                 |                   |                   |  |  |

|    | Bit position  Default | 11                                    | 10                   | 9                 | 8                 | 7                                                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                | 4        | 3                 | 2                 | 1                 | 0                 |  |  |